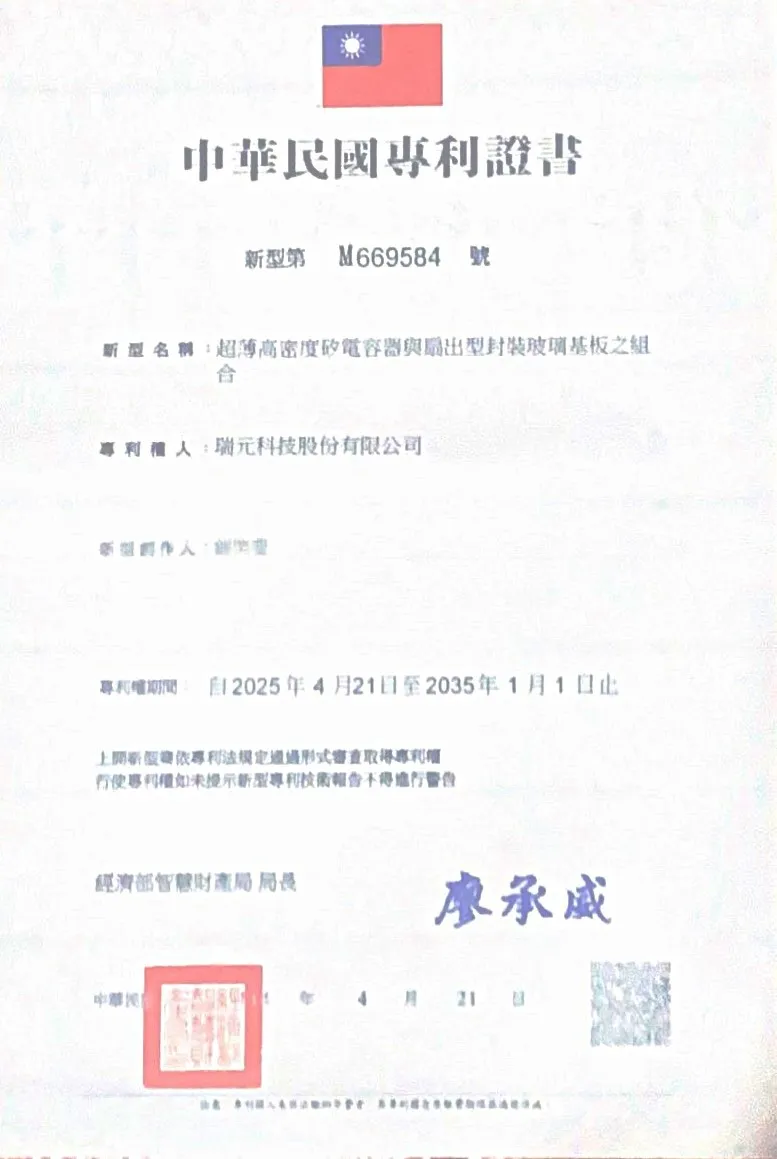

Combination of Ultra-Thin High-Density Silicon Capacitors and Fan-out Packaging Glass Substrate

This innovation combines Ultra-Thin High-Density Silicon Capacitors (UTHDSCs) with fan-out packaging glass substrates to enhance electrical performance. By embedding UTHDSCs within or near the Redistribution Layer (RDL), it optimizes power distribution and reduces parasitic inductance, making it ideal for high-frequency electronics like 5G, AI accelerators, and automotive systems while improving structural reliability and thermal management.

As chips become faster, they suffer from power instability and signal noise. While glass substrates offer superior electrical properties, they are mechanically fragile and prone to cracking. Furthermore, traditional capacitors are too bulky to be placed near the chip core, leading to significant high-frequency noise and heat dissipation challenges in advanced semiconductor packages.

The solution integrates ultra-thin silicon capacitors directly into the glass substrate structure via advanced through-holes and interconnects. By placing high-density capacitance as close as possible to the chip, it provides instantaneous voltage compensation and minimizes parasitic inductance. This integration also reinforces the mechanical robustness of the fragile glass substrate while leveraging its low dielectric loss for better thermal performance and signal integrity.

It solves the dual flaws of "mechanical fragility" and "high-frequency decoupling difficulty" in glass substrates. Prior art struggled to integrate high-capacity decoupling without increasing package thickness. This invention overcomes these reliability bottlenecks by co-designing UTHDSCs with the RDL, addressing the power noise issues common in 5G and AI chips while making glass-based packaging commercially viable.

High capacitor density and ultra-thin design: Saves vertical space, supporting thinner and lighter chip modules.

Low parasitic inductance (ESL): Significantly reduces voltage ripple and noise, maintaining high-frequency stability.

Strengthened mechanical structure: Embedded capacitors distribute stress, reducing the risk of glass substrate breakage.

Excellent thermal management: Combined with the high thermal stability of the glass substrate, overall reliability is improved.

Industries where the invention can be useful?

5G/6G Communications: High-frequency radio frequency (RF) modules. Artificial Intelligence (AI): High-performance processors and AI accelerators for data centers. Automotive Electronics: Advanced Driver Assistance Systems (ADAS) and Electronic Control Units (ECUs). Aerospace and Defense: Stable electronic components for high-temperature and high-vibration environments.An estimate of the total addressable market?

$40 billionPotential Customers/End Users. Who might benefit?

Wafer foundries and packaging/testing companies: TSMC, Intel, ASE. High-performance computing chip designers: NVIDIA, AMD, Google. Automotive supply chain: Tesla, Bosch.Documents

-

1766221961955_895.pdf

Actions

Added all portfolio

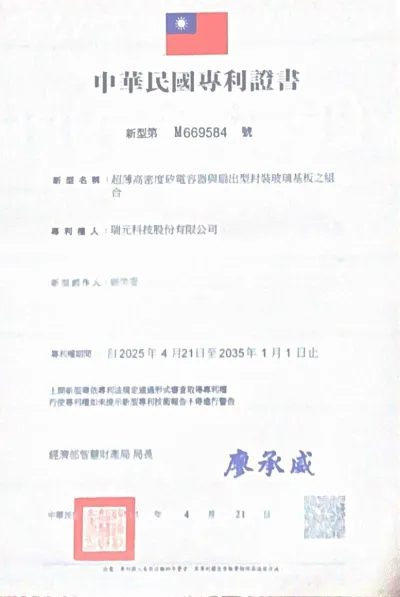

| Country | Current Status | Patent Application Number | Patent Number | Applicant / Current Assignee Name | Title | Google Patent Link |

| Taiwan | Issued | M669584 | TWM669584U | Dollarchip Technology Inc. | Combination of ultra-thin high-density silicon capacitors and fan-out packaging glass substrate | Google patent link |

You may also like the following patent